|

그냥남자사람

추천 176

조회 262084

날짜 2021.09.24

|

|

그을음

추천 59

조회 75009

날짜 2021.09.24

|

|

허무주의

추천 222

조회 190141

날짜 2021.09.24

|

|

되팔렘꼴통절단기

추천 20

조회 51147

날짜 2021.09.24

|

|

S.A.T.8

추천 8

조회 12874

날짜 2021.09.24

|

|

핵인싸

추천 920

조회 413258

날짜 2021.09.24

|

|

별빛 단풍잎

추천 5

조회 16674

날짜 2021.09.24

|

|

찐쿠아

추천 19

조회 28015

날짜 2021.09.24

|

|

Jade_2

추천 40

조회 179700

날짜 2021.09.24

|

|

닭도리탕 비싸

추천 26

조회 58626

날짜 2021.09.24

|

|

유우타군

추천 22

조회 62980

날짜 2021.09.24

|

|

가챠하느라밥이없어

추천 3

조회 5869

날짜 2021.09.24

|

|

니미핸드릭스

추천 28

조회 37756

날짜 2021.09.24

|

|

길가에e름없는꽃

추천 2

조회 8641

날짜 2021.09.24

|

|

루리웹-2122312666

추천 144

조회 69487

날짜 2021.09.24

|

|

긴박락

추천 3

조회 9054

날짜 2021.09.24

|

|

타카가키 카에데

추천 13

조회 17300

날짜 2021.09.24

|

|

꼬르륵꾸르륵

추천 3

조회 14200

날짜 2021.09.24

|

|

등대지기 공대생

추천 0

조회 9465

날짜 2021.09.24

|

|

no.777

추천 6

조회 14028

날짜 2021.09.24

|

|

루리웹-7309663092

추천 66

조회 61020

날짜 2021.09.24

|

|

이사령

추천 15

조회 20012

날짜 2021.09.24

|

|

달걀조아

추천 4

조회 7568

날짜 2021.09.24

|

|

얼

추천 3

조회 5965

날짜 2021.09.24

|

|

MK.II

추천 7

조회 12460

날짜 2021.09.24

|

|

고수달.

추천 3

조회 11998

날짜 2021.09.24

|

|

『EDEN』

추천 3

조회 5142

날짜 2021.09.24

|

|

Julia Chang

추천 74

조회 35289

날짜 2021.09.24

|

본문

BEST

자동화 기능이 이미 있긴 한데 불도저 1세대에서 검수할 사람이 많지 않아서 대부분 자동 돌렸다가 개망함

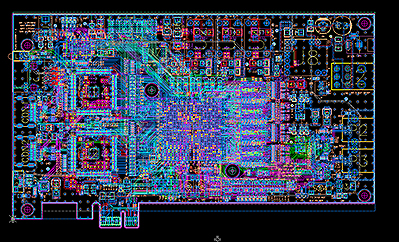

인텔은 모래로 만들고 암드는 아트로 만드는 구나!

사천성

이미 그 기능은 있지만 또 전선별 전기적 특성 때문에 결국 사람이 손대주고 고려해야할 부분이 많아서...

누님이 손으로 꾹 눌러서 만드는 거 아니었어?

ICC나 Innovus나 실제로 써보면 생각대로 라우팅을 안해줌 예전엔 셀딜레이만 신경쓰면 됐다지만 미세공정 가면서 넷딜레이도 엄청나게 커지는데 그거 신경쓰면서 하다보면 사람 손이 안탈수가 없음

사람이 하는거 아니야... 베릴로그로 짜면 공정별로 합성해주는 컴파일러같은게 있음 물론 cpu같은 영혼갈아서 만드는 것들은 사람이 좀 손보긴 함.

복잡도 생각하면 음... 트레이닝 데이터를 뭐로 넣어줄거냐가 문제지 ㅋㅋㅋㅋ

그거는 품질검사 필증 붙일때고

이거 인공지능 돌리면 간단하겠네

이미 그 기능은 있지만 또 전선별 전기적 특성 때문에 결국 사람이 손대주고 고려해야할 부분이 많아서...

랑이비

자동화 기능이 이미 있긴 한데 불도저 1세대에서 검수할 사람이 많지 않아서 대부분 자동 돌렸다가 개망함

랑이비

ICC나 Innovus나 실제로 써보면 생각대로 라우팅을 안해줌 예전엔 셀딜레이만 신경쓰면 됐다지만 미세공정 가면서 넷딜레이도 엄청나게 커지는데 그거 신경쓰면서 하다보면 사람 손이 안탈수가 없음

자동화 후 사람이 최적화 해야 그나마 구실함 ㅋㅋㅋㅋ

실제로 요즘 설계는 인공지능이 어느정도 해주고 사람이 보정해주는 식으로 함

자동 돌려서 불도저 불남

인텔은 모래로 만들고 암드는 아트로 만드는 구나!

딥러닝으로 설계하면 어떨까

나래여우🦊

복잡도 생각하면 음... 트레이닝 데이터를 뭐로 넣어줄거냐가 문제지 ㅋㅋㅋㅋ

구글에서 플로어플랜은 ai로 했다고 최근 뉴스가 나왔자

floorplan이 뭔지 제대로 알아보자

사실 본문 짤은 보드/패키지 설계 쪽이고 플로어플랜은 탑 레벨 pnr할 때 블럭들 라우팅 리소스/PDN 생각하면서 배치하는거지 구글에서 TPU 설계할때 AI로 했다고 최근 뉴스로 한참 뜨더만 마치 ai가 전부 한것처럼 말하긴 했다만...

내 생각에는 가장 인간의 의지가 많이 반영되는 단계가 floorplan이라 생각하거든.. 그렇다고 itenery 하는데 ai가 또 못할건 없을것 같기도 하고..

뉴스에선 구글이 그거로 이득 봤다고 하는데 사실 잘 모르겠음 실제 배치 하다보면 메인 기능이 붙는 로직과 테스트 로직 같은거 분리해서 배치해야하고... 탑 레벨에서 블럭 간 조합할 땐 괜찮을거 같은데 IP 레벨에선 과연? 이란 생각이 들긴 하더라

시그널 노이즈 위주로 볼지, 동작 노이즈를 볼지, 아니면 파워를 볼지, 아님 칩사이즈가 중요한지따라서 배치를 고려해야지 않겠음? 칩사이즈가 중요하다면 테스트모드랑 실제동작블럭이랑 같이 묶어둬야지 테스트라인들로 메탈떡판칠거 아니면.. 생각보다 cu가 리쏘할때 오염도가 심해서 메탈은 density 생각해서 써야하거든..

난 더미필 PDK를 믿어 ㅋㅋㅋㅋㅋㅋㅋㅋ hsi IP하는 입장에선 cts 측면땜에 분리하는게 좀 있는듯 지터랑 듀티 특성 본다고 주요 cts는 거의 독립시켜 놓고 상대적으로 중요성 떨어지는 테스트 로직은 클럭 게이팅 넣고 하고 하다보니... 우웨엑...

HSI하면 당연 가드링을 해야지. 더미FILL 믿음 큰코다친다. 벌크노이즈가 생각보다 크기때문에 DNWELL 넣고 가드링 빡세게 둘러쳐야함. 그리고 아마 PHY하는것 같은데 ESD 잘 넣고. ESD가 시그널 다 잡아먹음. 파워소모도 있고.

이제 3년차 신입 나부랭이라 시키는것만 하고 있지 뭐... 난 디지털이라 아날로그 IO쪽까진 잘 모르는데 아날로그 IO 받아서 implementation 하다보면 신경 쓸거 엄청 많긴 하더라고

벌크의 레벨을 바꿀정도의 노이즈가 1. 클러킹 노이즈 2. 시그널 노이즈 요 두개인데, 클러킹 노이즈는 ff에서도 많이 영향이 생기니깐 디지털, 아날로그로 나누던가 아님 파워도메인 으로 나누던가 해서 가드링 빡세게 연결하자고 하면 좋은 자세라고 조ㅗ아해줌.

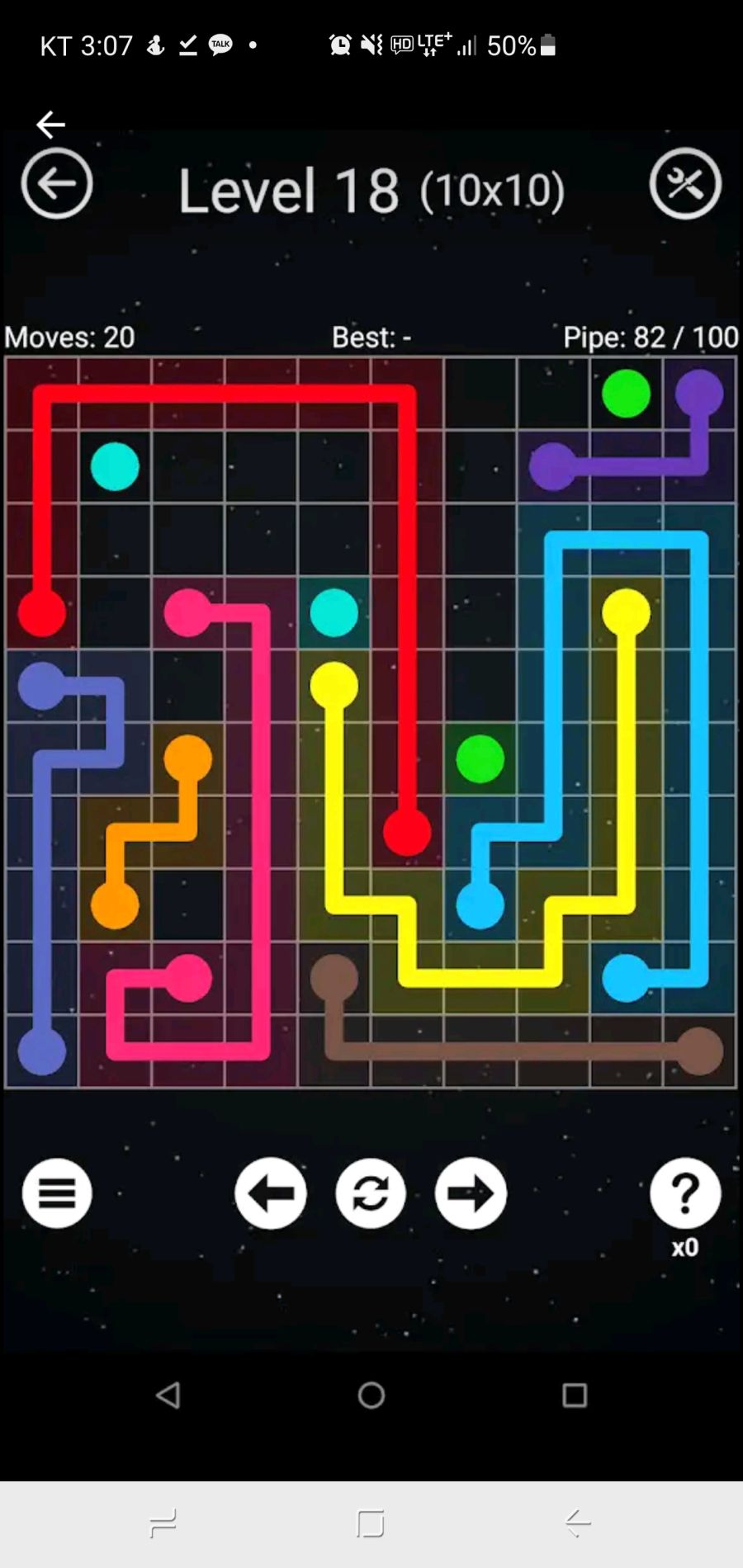

저 퍼즐 게임 재미있어보인다

천재들이 저거 프리랜서로 잘 그려서 판다는 소리는 있었지

접촉사고!~

사천성

거상할때 이거 자주 했는데 ㅋㅋ

루리웹-1968637897

이 이걸 알다니.... 아재......

거상할때 이꼬라지 날때가 제일 싫었어...

브금이 아직도 들리는거같다 한자공부하기 딱좋은 브금

꼬꼬마시절 이것만 하면 최고 기록이다!헸는데 꼭 저거걸림 ㅋㅋ

멘토 VX같다ㅋㅋ

저 퍼즐겜 이름이 뭔데?

icfb

와...

누님이 손으로 꾹 눌러서 만드는 거 아니었어?

[文派]_ksrg

그거는 품질검사 필증 붙일때고

칩설계로 들어가면 진짜 토나올 듯

사람이 하는거 아니야... 베릴로그로 짜면 공정별로 합성해주는 컴파일러같은게 있음 물론 cpu같은 영혼갈아서 만드는 것들은 사람이 좀 손보긴 함.

PnR봐가면서 실제로 STA하는 입장에서 보면 손 겁나 감 ㅠㅠ

우리회사 pnr은 존나 안해줘서 짜증....

STA하다가 아무리봐도 딜레이가 이리 안나올텐데 하고 보면 라우팅이 아주 산으로 가있음 수정해달라고 했는데 수정이 안됨 아니 쉬뻘!

수백 수천개의 소자면 cpu 다이 이야기는 아닐 것 같고... cpu 다이 올릴 기판의 설계인가...?

시퓨 내부도 따지고 보면 저런식임. 결국mosfet 소자라 회로 이어야해서... 그런데 사진 찾아보면 저렇게 멀리 연결하는건 거의 없어서 비슷한 패턴이 반복되서 보이는데 이것도 굉장히 멋짐... 예전에 인텔에서 사진 많이 풀었던거 기억하는데 찾아보려니 안보이네요..

전자기사딸때 해봤는데 orcad로 회로만들고 그거 앞뒤면 서로 안겹치게 양면으로 설계하는거 잼씀

기본은 툴이 자동으로 해주는게 맞지만 사람이 만져서 최적화 해주는것도 중요한데 여기서 몸값 크게 갈림

풀커스텀 레이아웃은 진짜 어찌하나 싶더라 ㅋㅋㅋㅋㅋ

그럼 짐켈러는 저 회로도 최적화를 기가막히게 해내는 사람인가?

잘 모르지만 저 회로도 최적화도 어느정도 할줄 알겠지만 그보다는 연산기를 어떻게 얼마나 배치할까 이런거에 대한 전문가일껄

아아... 난 대학다닐때 졸업작품 만든다고 기판설계부터 다 했는데

첫번째 그림은 개소리고 위로 넘어다닐 수 있음

그리고 모두 안겹쳐야 하는게 아니라 몇개는 같이 쓰는것도 있음

더 덧붙이면 저걸 그리는일은 쉬움 문제는 저 그림이 제대로 동작 하느냐를 알아야 하는데 그게 시간이 오래 걸리고 어려움

구조를 어떻게 짜느냐에 따라서 성능이 갈리는 분야의 경우엔 AI로 돌리더라도 사람 손으로 고쳐야됨. 시뮬레이션을 하기전까지는 AI는 성능을 알 수 없는데 사람은 직감적으로 알 수 있는 부분이 있거든.

실제로 저렇게 간단하지 않습니다 모스펫은 분명 스위칭이 확실한 소자라 설계가 편해진건 맞지만 기생커패시턴스, 기판외 길이당 인덕턴스까지 고려해서 PLL의 설계까지 해야합니다 퍼즐같은게 아니라 복잡한 공식으로 전류를 계산하거나 동작여부확인을 위해 시뮬레이션을 돌려야하는 극한의 정신노동입니다

실제로 리사 수가 CEO가 아니라 사내에서는 닥터로 불린다고 하던거 같던데...

조금은 사이즈가 큰 선놀이 라고 읽고 갈아먹는다.

영혼이 맑아지는 선정리네요

이번에 컴하나 살까하는데 선정리좀

이건 채널이라고 해서 선길이가 이미 시그널 웨이브길이를 넘어서기 때문에 반도체랑은 상관없음.

리사쑤 누님은 번개숨결로 모래를 콰아아아아아! 하면 나노 공정 대는걸로 알았는데....

기본적으론 넷리스트 다 구별되서 사람이 해줄건 검수랑 오류 수정 정도겠지. 라고 하고 그게 TOP. 세세하게 파고들어가면 그라운드 층 나누고 전압층 나누고 기판 층간 간섭도 고려하고…하겠지만 결국 마지막엔 다 납땜임….납땜…..

팩토리오 생각난다

나 저게임 존나 잘하는데

게임 제목이 뭐예요??

앱스토어에 FLOW FREE라고 치면 무료버젼 겜 나옴

여기...

와! PCB! OR캐드!

뭔가 조금씩 아는데 하나씩 부족한듯 써놨네.. 아래에 그럴싸한 그림은 칩설계가 어니고 pcb artwork 이고 우리가 받아보는 그래픽카드 기판같은 커넥션 정보가 피지컬하게 그려진것임. 댓글중에 누가 얘기한데로 RLC를 추출해서 크로스커플링이라던가 시그널딜레이, 시그널 감쇄등을 시물레이션해서 미리 성능을 예측함. PCB ARTWORK에 보면 칩들어갈 자리가 보이는데, 그 칩들은 CMOS기반으로 설계한뒤에 MASK제작을 위한 layout 으로 변화는것이 기본 설계과정임. cmos로 설계하면 나중에 커스텀하기 쉽지만, cpu같이 알고리즘이 복잡하게 동작하는 기능을 구현하기엔 부적합해서 verilog같은 description으로 RTL레벨로 설계하는데, 이 구문표ㅕㄴ을 실제 cmos동작으로 전환시켜주는 합성과정을 거쳐야 하고 pdk라고 하는 공정에 기반된 피지컬한 디자인킷을 이용해서 치환시켜주는 작업을 뜻함. 당연 피지컬 디자인 이후에도 매뉴얼로 커스텀작업을 해줘야하고, 이것도 세대를 거치면 풀커스텀도 가능하게 되는데 이게 그 칩의 성능과 단가 경쟁력이 되기때문에 중요한과정임. 이게 생각보다 중요한데, 울나라보면 ai칩이든 arm칩이든 뭐든 척척 설계 한다고 하는데 생각보다 성능이 안나오는 이유가 풀커스텀 능력이 많이 딸림. 레이아웃 gds도 찬찬히 뜯어보면 로직컬하게 동작하는게 보이고 아날로그 설계한다 하면 레이아웃만 봐도 회로의 특성이 보인다. 그리고 위에 누가 얘기했는데 피지칼디자인 이후에 보이는 parasitic rc값이 중요하다고 하는데 성능에 따라서 다르고 그 기생값들이 없다라도 여러가지 테크닉으로 극복가능함. 다만 1ns 이하의 주파수에서나 통하고 그 이상이라면 다양하게 고려해야함

님 말이 맞는데 그렇게 적으면 아무도 날 봐주지 않아

남에게 인정받는 욕구는 중요하지.. 킹치만 틀린걸 고쳐주는 욕구라면?

욕구는 옳지

심심한데 아는거 주욱 적어보는거지 시간도 별로 안걸리고.. 저렇게 씹덕마냥 아는걸 주욱 적는게 의미있는게, 이분야 보면, 다들 전문성은 있다고 하는데, 저런식으로 전체과정을 한큐에 꿰는 사람은 잘 없더라.

사실 잘 모르는거 글 썼을 때 알려주는 유게이 댓글이 넘 좋아

삭제된 댓글입니다.

트레이너베지터

아니라서 대충 적었는데 문제라도?

회로 노잼임

와 신기하다…저걸 또 어캐 양산을하지