- 들어가기에 앞서, 이 글은 현업 6년차 학사 나부랭이의 지식이기 때문에 틀린 내용이 있을 수 있습니다

틀린 내용이 있다면 댓글로 지적해주시면 감사하겠습니다

이건 반도체 칩 수명에 대한 이야기

https://bbs.ruliweb.com/community/board/300143/read/68958241

컴퓨터 등지에 관심이 있다면 한 번 쯤 오버클럭, 팩토리 오버, 언더볼팅 등등에 대해 들어본 적이 있을텐데,

그게 대체 뭐고 왜 되는가에 대한 설명

비유해서 설명하기엔 내 지식이 모자란고로 그냥 담백하게 설명하겠읍니다

- 반도체 회로 코너란?

반도체 회로 설계를 했으면, 회로도로 꾸린 걸 실리콘 기반의 칩까지 생산하기 위한 회로 설계 도면(gds/oasis)을 만들어야 한다

그럼 여기서 이 회로가 실제로 동작하게 하기 위해 여러가지 요소를 고려해서,

내가 원하는 결과가 나오는지 시뮬레이션을 돌려가며 회로를 수정하게 되는데,

여기서 코너라는 개념이 들어간다

코너란게 뭐냐면, 반도체 칩 생산 과정에서 발생하는 성능 편차와 동작 환경에 따른 성능 편차 정도로 설명할 수 있다.

칩 생산 과정에서 발생하는 코너는 크게 Process Corner(트랜지스터 생산 공정에 따른 편차)와 Parastic(PEX) Corner(금속 선로 생산 공정에 따른 편차)가 있고,

동작 환경에 따른 코너는 크게 Voltage Corner(공급 전압에 따른 성능 편차)와 Temperature Corner(동작 온도에 따른 성능 편차)가 있다.

그래서 PVT + PEX 코너라고 많이 일컫는다

조금 더 깊게 들어가서 설명하자면,

- Process corner는 트랜지스터 생산 과정 중, n/p타입 반도체를 만들기 위해 주입하는 도핑 물질의 농도 차이 등에 의해 반도체의 성능을 결정짓는 중요 요소인 트랜지스터의 on/off 기준 전압(문턱 전압)이 달라져서 발생

=> 문턱 전압이 낮으면 속도는 빠르지만 전력을 많이 먹고(Fast corner), 문턱전압이 높으면 반대(Slow corner)

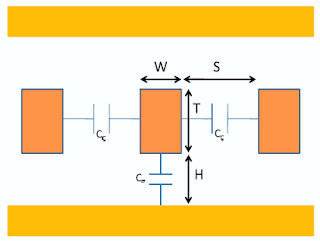

- Parastic/PEX corner는 생산 과정 중 금속 선로의 두께, 옆 금속 선로와의 거리 등에 의해 금속 선로의 저항과 인접 금속 선로 사이에서 생기는 기생 커패시터 차이에 의해 발생

=> 금속 선로가 두꺼우면 저항은 낮아지지만 인접 금속 선로와 거리가 가까워져서 기생 커패시터는 커지고 얇으면 반대

=> 반도체 회로에 사용되는 금속 선로는 수십~수백 나노미터 수준의 두께이기 때문에 학창시절엔 늘 무시하곤 하는 회로 선로 저항을 절대 무시할 수 없다

- Voltage corner는 모종의 사유로 공급 전압 자체가 낮게 들어오거나, 혹은 동작 중 전력 소모가 급격하게 변해서 공급 전압이 출렁이는 경우에 의해 발생

=> Dynamic voltage drop(DVD, 혹은 Dynamic IR drop), IR drop 등 전력 소모 - 패키지/보드/칩 자체 전력 공급 망에 의해 발생하거나

=> 전력 반도체, 전력 공급 컨트롤 칩(PMIC) 자체의 성능 편차에 의해 발생

- Temperature corner는 동작 시 주변 온도/자체 온도에 따라 발생

=> 기본적으로 전류가 흐르는 양 = 성능은 온도에 비례. 온도가 너무 낮으면 이온화가 덜 되므로 전류를 옮기는 매체인 캐리어(전자+정공)가 적어서 성능이 낮아진다

=> 근데 또 너무 높으면 캐리어 자체는 충분하긴 한데 원자핵과 부딪히는 횟수가 늘어나서 또 성능이 일정 이상 올라가진 않는다

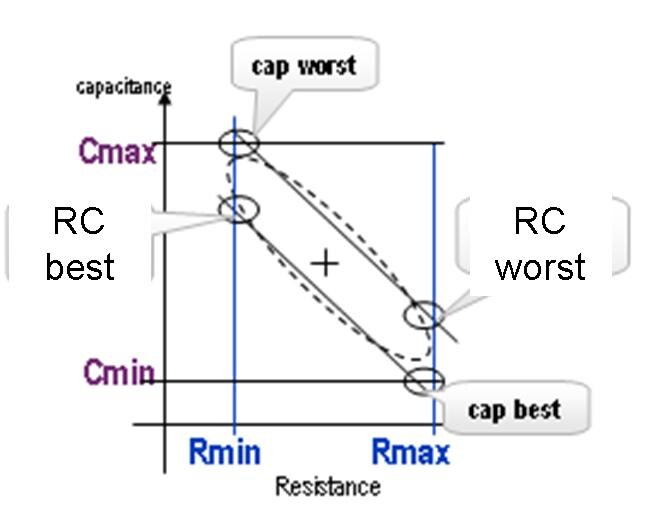

아래 그림은 Process corner와 PEX corner에 대한 그래프다

(1) Process corner

보통 현세대 반도체는 정공을 캐리어로 하는 PMOS와 전자를 캐리어로 하는 NMOS의 조합으로 만들어져서, 두 개가 모두 빠른 경우/모두 느린 경우/한 쪽만 빠르고 느린 경우로 나뉜다.

이를 각각 FF(둘다 빠른 경우), SS(둘다 느린 경우), TT(둘다 표준값), FS(P는 빠르고 S는 느리고), SF(P는 느리고 N은 빠르고)라 한다.

여담으로 말하자면, 실제로 칩 하나에 들어가는 수십억개의 트랜지스터가 모두 극단적인 slow/fast 쪽에 몰려있을 수는 없다.

(실제로 정규 분포를 완벽히 따르진 않겠지만, 정규 분포를 따른다 가정할 때, 3시그마 기준, 트랜지스터 하나만 보자면 최하의 성능을 낼 확률이 약 0.3% 정도지만, 칩 전체로 봤을 때 모든 트랜지스터가 최하의 성능을 낼 확률은 3시그마는 커녕 6시그마도 벗어난다.)

따라서 실제 설계를 할 때는 이를 고려하여 설계를 하는데, 이 과정에서 칩 내부에서 발생하는 분포 자체는 보상할 필요가 있다.

이를 OCV, On-chip Variation이라 하며, 시뮬레이션을 수행할 때는 이를 통계학적으로 접근하여 이 분포를 반영한다.

예시를 들면, 극단적인 SS 트랜지스터의 성능을 0이라고 했을 때 칩 설계 할 때는 전반적인 트랜지스터가 20 정도의 성능을 가진다고 체크하되, 그 20도 모두 20이지는 않고 언놈은 0까지 가는 경우가 있다는 걸 통계학적으로 분석하여 반영한다.

이게 그 합성이든 pnr이든 STA(static timing analysis)든 타이밍 체크 해본 사람이라면 한번쯤 들어봤을 법한 OCVM(On-Chip Variation Methodology)다

(출처 : https://www.vlsi-expert.com/2012/02/parasitic-interconnect-corner-rc-corner.html)

(2) PEX corner

복잡하게 설명했지만 결론만 말하면 실제 칩 생산 과정에서 변수가 많다보니, 언놈은 태생 자체가 느리고 언놈은 태생 자체가 빠르고, 또 동작 환경에 따라 성능이 다르다는 이야기

3줄 요약

- 반도체 생산 과정/동작 환경에서 오는 차이때문에 성능 편차(코너)가 발생한다

- 생산 과정의 코너에는 process corner와 pex corner가 있고

- 동작 환경의 코너에는 voltage corner와 temperature corner가 있다

- 회로 설계의 마진과 오버 클럭

반도체 회로 설계를 하며 어떤 회로를 개발을 하면 당연히 목표한 스펙이 있을거고,

당연하지만 이 설계 과정에서 앞서 서술한 반도체의 모든 코너에서 내가 목표한 스펙을 맞춰야지 칩을 생산했을 때 최대 수율을 확보할 수 있을 것이다.

100개를 생산했을 때 100개가 어떤 코너로 생산될지 모르고, 또 생산한 칩이 어떤 환경에서 동작할지 모르는 상황에서,

최대한 많은 칩이 정상적으로 동작 하게하려면 모든 코너에서 정상 동작하는 걸 확인해야 한다.

그래서 반도체 설계를 할 때는 이런 모든 편차를 고려해서 시뮬레이션을 돌려 검증해가며 설계를 하게 된다.

(더해서 이런 편차 뿐만 아니라 추가 마진을 넣는 경우도 있다)

그럼 여기서 생각해볼 수 있는게

가장 성능이 안좋은 코너를 기준으로 기준 스펙을 맞췄으면, 성능이 좋은 코너에서는 기준 스펙보다 더 높은 스펙으로 동작할 수 있겠네?

이게 오버클럭/언더볼팅의 기본 골자가 된다.

즉, 100의 성능을 타겟으로 해서 가장 성능이 안좋은 코너에서 100의 성능으로 동작하게끔 회로를 설계했으니,

가장 좋은 코너에서는 실제로는 120, 130으로 동작할 수도 있거나(오버클럭)

혹은 동작 환경을 좀 더 악화시켜도(공급 전압을 낮춰도) 100에서 동작하는 것(언더볼팅)

이게 오버클럭하는 사람들이 일반적으로 말하는 '수율'이다. (성능 마진이 얼마나 남아있나?)

이건 뉴스에서 종종 나오는 (생산) 수율과는 다르다. 생산 수율은 100개를 뽑았을 때 몇개가 정해진 스펙대로 동작하느냐? 의 문제이다.

(오버클럭/언더볼팅에서 말하곤 하는 수율은 보다 정확하겐 마진 정도로 표현하는게 맞을 듯 하긴 하다)

쪼끔 더 깊이 들어가면 ASV, Adaptive Supply Voltage라고 칩의 process corner를 확인해서 성능이 구린 놈은 전압을 더 먹여서 성능을 맞추고, 성능이 좋은 놈은 전압을 낮춰서 전력 소모를 낮추는 기법도 있다.

(이를 위해 칩의 process corner를 확인하는 회로를 넣는다)

3줄 요약

- 반도체 회로 설계를 할 때는 상기한 코너를 염두에 두고 설계한다

- 가장 안좋은 코너에서 정상동작하는 것을 고려하고 설계한다

- 그러므로 가장 좋은 코너에서는 정해진 스펙보다 더 좋은 스펙으로 동작할 가능성이 있다

다만 당연하지만, 기업은 생산 수율을 극대화 시키는 쪽을 방향으로 잡는다.

즉, 성능 편차를 최대한 줄이는 방향으로 나아가는 셈. (오히려 성능 편차가 크면 설계 난도가 더 높음)

기존에 성능 편차가 큰 상태에서 마진 많이 먹여가며 설계를 했던 제품이,

나중에 공정 안정화가 되면서 마진이 많이 남게 되어 오버가 잘 들어가는 경우가 '몇 주차 이전 제품은 오버 잘 들어가요' 하던 그런 개념.

(공정 개선이 되었으니 마진 빼서 설계 리비전 했지 않을까?)

당연하지만 마진을 포함해서 설계를 하면 설계 난도가 올라가고 이 마진을 커버하기 위한 추가적인 요소가 들어가 면적 측면에서 아무래도 불리하기 때문에 생산 단가 측면에서 마이너스가 된다.

그렇군요