|

이지스함

추천 0

조회 2

날짜 22:41

|

|

영국의아침식사

추천 0

조회 2

날짜 22:41

|

|

Not4Sale

추천 0

조회 18

날짜 22:40

|

|

유준

추천 0

조회 5

날짜 22:40

|

|

Mati

추천 0

조회 1

날짜 22:40

|

|

xnest

추천 8

조회 81

날짜 22:41

|

|

Elpran🐻💿⚒️🧪🐚

추천 5

조회 82

날짜 22:40

|

|

하즈키료2

추천 1

조회 29

날짜 22:39

|

|

사시미오

추천 1

조회 68

날짜 22:39

|

|

이지스함

추천 1

조회 61

날짜 22:40

|

|

에이다웡

추천 4

조회 60

날짜 22:40

|

|

은시계

추천 5

조회 118

날짜 22:39

|

|

BoomFire

추천 4

조회 56

날짜 22:40

|

|

책중독자改

추천 13

조회 214

날짜 22:40

|

|

루리웹-3507363516

추천 0

조회 25

날짜 22:40

|

|

Skullcrushers

추천 0

조회 20

날짜 22:39

|

|

Fei_Allelujah

추천 0

조회 40

날짜 22:40

|

|

THE·O

추천 12

조회 350

날짜 22:39

|

|

분뇨의질주

추천 12

조회 663

날짜 22:38

|

|

우유튀김

추천 2

조회 112

날짜 22:38

|

|

주똥구리

추천 2

조회 78

날짜 22:39

|

|

나래여우🦊

추천 0

조회 37

날짜 22:38

|

|

혐오의 정구지

추천 0

조회 23

날짜 22:38

|

|

게데베데

추천 0

조회 26

날짜 22:38

|

|

토와👾🪶🐏

추천 12

조회 252

날짜 22:38

|

|

st_freedom

추천 0

조회 48

날짜 22:38

|

|

책중독자改

추천 10

조회 343

날짜 22:38

|

|

용사님

추천 5

조회 262

날짜 22:38

|

삼성은 ㅂㅈ 가없었구나

냉각은 어떻게하려나

그건 메모리 자체를 생산하는 방식이고 HBM은 대역폭을 늘리는 방향을 핀당 전송속도를 늘리는게 아닌 핀개수를 늘리는 방향으로 잡은거

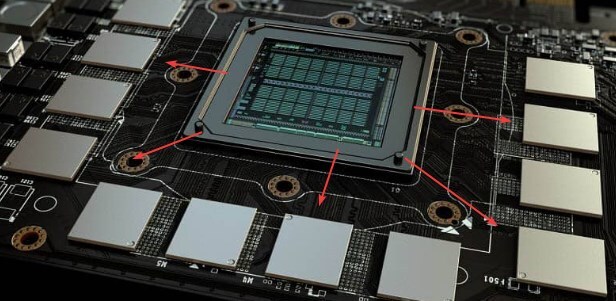

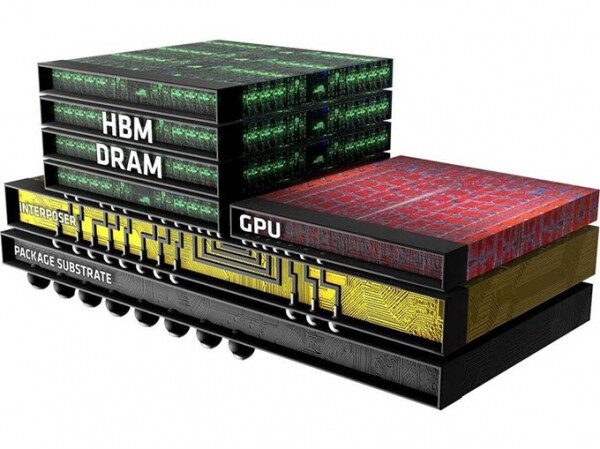

일반적인 DDR, LPDDR, GDDR의 경우 채널당 칩 하나가 할당되고 여기에 데이터핀 개수가 16개~32개 수준에 다른 핀 다 합쳐도 40여개 수준인데 HBM은 HBM3 기준 채널당 64개 +@에 칩 하나에 16개 채널이 묶여있음. 그래서 데이터핀만 1024개, 커맨드 어드레스 핀까지 더하면 거기서 +@ (기억 상 채널당 리페어용이나 다른 목적을 위한 핀까지 다 합치면 아마 100개 쯤 될거) 근데 이렇게 많은 신호를 기존 패키지/PCB에서 신호 선로를 연결하는 건 불가능에 가까움. 그래서 여기서 같이 나온 기술이 실리콘 인터포저, 2.5D 인터포저로 반도체칩 생산 공정의 BEOL(금속 배선) 공정을 갖다가 씀. 일반적인 메모리 - soc간 연결이 (soc 다이) - (soc 패키지) - (pcb) - (디램 패키지) - (디램 다이) 이 순이었다면, HBM의 경우 (soc 다이) - (인터포저) - (디램 다이) 이렇게 감. 이게 하나의 패키지가 되어있고

저거 높이는 어떻게 되는거야. 기존 보드에 들어가나?

높이도 제덱 스펙으로 정해져있음 그리 높지 않음