* 현업 6년차 학사졸 엔지니어 응애의 지식이라 잘못된 점이 있을 수 있습니다 지적 부탁드립니다

* 출처 같은데 들어가면 더 많은 정보를 쉽게 풀어썼으니 참조

으레 반도체 몇 나노 공정 몇 나노 공정하는데, 여기서 몇 나노미터의 의미를 알기 위해서는 우선 반도체 회로의 기본 소자인 트랜지스터의 구조에 대해 개략적으로 알아야함

트랜지스터는 일종의 스위치, 혹은 증폭기의 역할을 하는데, 현존 반도체 회로에서 쓰이는 대부분의 트랜지스터는 MOSFET, 메탈-옥사이드-실리콘 필드 이펙트 트랜지스터 구조를 채용하고 있음 (아래)

이 FET는 소스와 드레인, 그리고 게이트로 이루어지는데, 실제로는 훨씬 더 다양한 특성을 갖고 있지만 기본적인 스위치 동작을 보자면,

게이트에 일정 이상의 전압(=문턱 전압)이 가해지면 소스와 드레인 사이의 전자가 흐를 수 있는 길이 생겨 전류가 흐르는 구조임

이렇게 게이트에 어떤 전압을 가하냐에 따라 전류가 흐르고 안 흐르냐, 이 스위치끼리 연결하고 조합해서 최종적으로 만들어진 거대한 회로가 기본적인 반도체 회로의 구성이라고 보면 됨

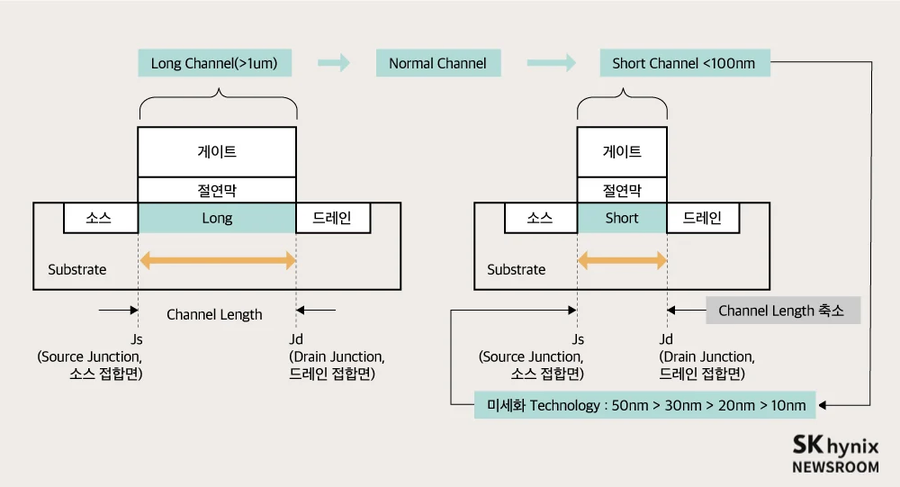

이 때 소스와 드레인 사이의 전자가 흐를 수 있는 길을 채널이라고 하며, 반도체 공정에서 말하는 몇 나노 몇 나노하는게 바로 이 채널의 길이를 말하는거였음

한 편, 트랜지스터에 흐르는 전류에는 여러가지 요소가 반영되지만 그 중 채널 길이에는 반비례함.

즉, 트랜지스터 자체의 크기를 줄여 채널의 길이를 줄이면, 보다 낮은 전압으로도 동일한 전류를 흘릴 수 있거나 동일 전압에서 더 많은 전류를 흘릴 수 있으므로 트랜지스터 자체의 성능이 좋아짐. (스위치 딸깍 눌렀을 때 좀 더 빠릿빠릿하게 반응한다고 생각하면 대충 맞음)

당연히 트랜지스터 크기가 작아지면 동일 면적에 더 많은 트랜지스터를 넣을 수 있으니 더 복잡한 회로를 구현할 수 있으니 성능이 좋아질 것이고, 반대로 유사한 복잡도의 회로를 더 작은 면적으로 구현할 수도 있으니 동일 성능 저 전력, 혹은 동일 전력 고 성능을 달성할 수 있게됨

그래서 저 채널 길이를 계속 줄여왔는데, 예상치 못한 문제를 마주한게 바로 숏채널 이펙트임

잠깐 근본적인 이야기를 하자면, 전류는 전자의 흐름인데, 반도체로 주로 쓰이는 실리콘은 기본 상태에서는 자유 전자/정공(합쳐서 캐리어라고 함)가 많지 않아 거의 전류가 흐르지 않는 부도체에 가까운 상태이고, 여기에 어떤 물질을 추가 도핑해서 캐리어를 늘려서 사용함

이때 어떤 물질을 사용해서 캐리어 중 전자를 메인으로 하느냐(N타입 반도체), 정공을 메인으로 하느냐(P타입 반도체)가 되는데,

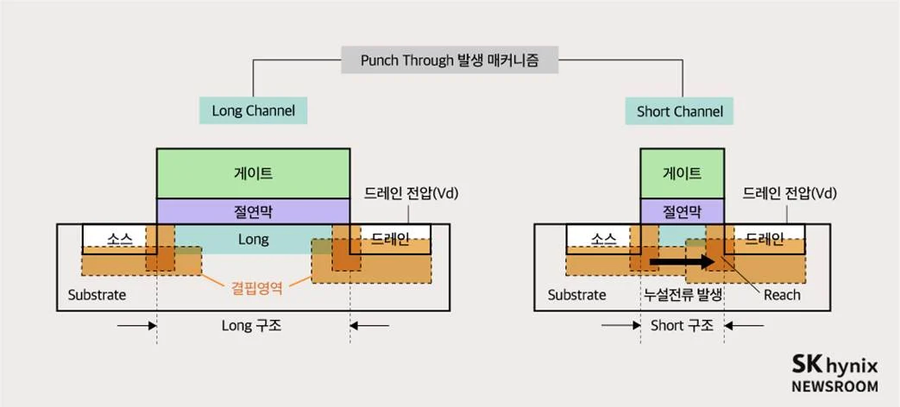

이 N타입과 P타입 반도체끼리 서로 맞붙었을 때 상호 에너지 밴드 차이로 인해 캐리어가 넘어갈만큼 넘어가고 더이상 넘어가지 않으면서 일종의 장벽(공핍층)이 만들어지고, 이 장벽에는 캐리어가 존재하지 않음

위에 일정 전압을 가했을 때 채널이 형성되며 전자(=캐리어)가 이동한다 했는데, 일정 전압을 가해 이 장벽을 허물어서 길이 생긴다고 생각하면 됨

여기서 문제는 이 놈의 공핍층인데, 드레인 전압(보통 신호는 게이트로 인가되고, 공급 전압이 드레인에 인가됨)이 올라가면 공핍층이 넓어짐

채널이 충분히 길 때는 공핍층이 넓어져도 문제가 안됐는데, 채널이 짧아지면서 공핍층이 넓어져 겹쳐버려 걍 전류가 질질 새버리는거임

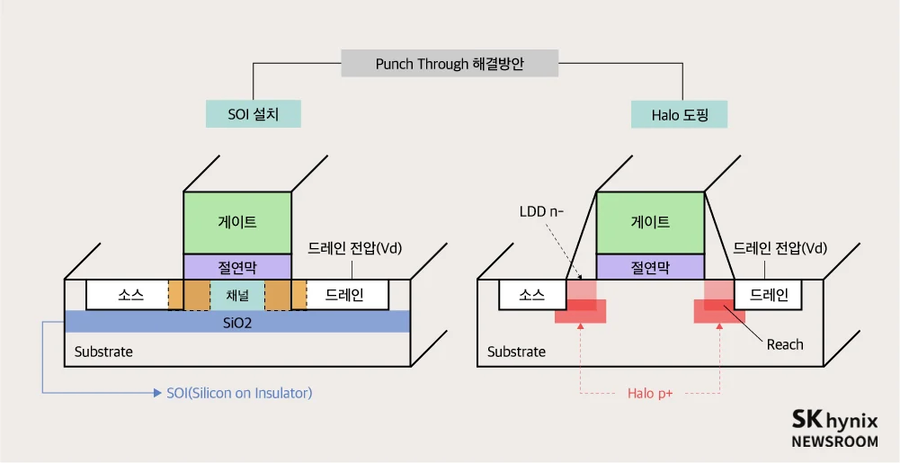

이 외에도 여러가지 문제가 존재했고, 여하튼 그간 사용되던 위와 같은 플래너펫 구조를 유지한 채로 채널 길이만 줄이는 것은 한계에 봉착함

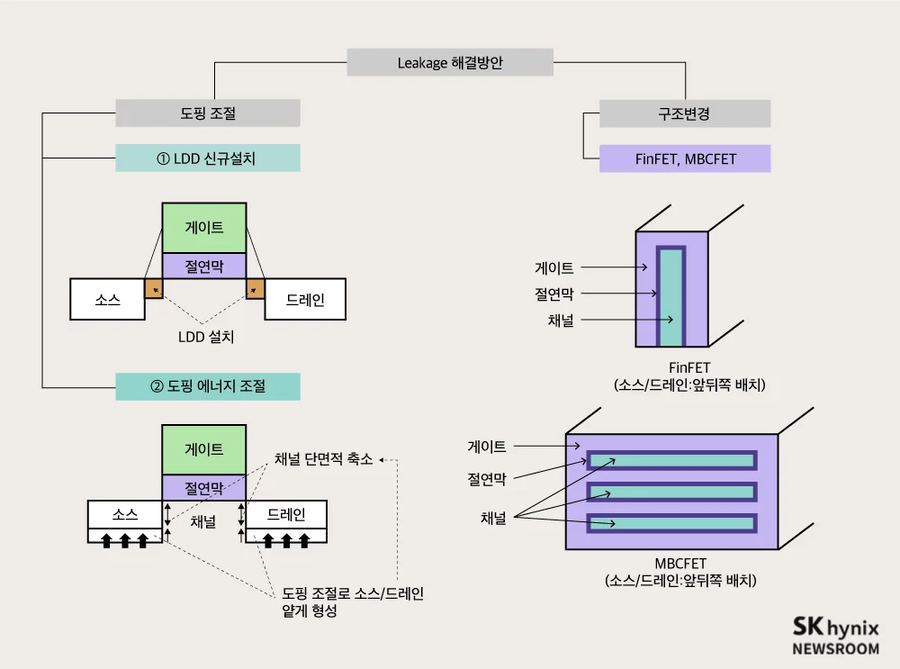

그래서 채널 길이는 어느정도 확보한 채로 반도체 성능은 올려야하니, 여러가지 방법을 도입하게 되는데,

위와 같은 FDSOI나 한번쯤 들어봤을 핀펫이나 GAA 같이 구조 자체를 바꿔서 트랜지스터 성능을 향상시키게 됨

여기서 아리까리해진게 기존엔 채널 길이가 진짜 소스-드레인 간 채널 길이 나타냈고 그게 곧 반도체 미세 공정의 세대/성능의 척도였음

근데 이제 성능 자체는 향상됐으나 물리적인 채널 길이는 그대로니 그걸 나타내기가 애매해진거임

어쨌든 그래도 기존 관습은 남아있으니, 대신 기존 스케일링 공식 (반도체 채널 길이와 성능 간 비례 공식)을 그대로 따라서

아 이게 기존 구조를 유지했으면 채널 몇 나노짜리랑 동급 성능을 가진 트랜지스터 공정이에요 ㅎㅎ 이렇게 된거

즉 3나노라고 해서 실제 채널 길이가 3나노인게 아니라, 채널이 충분히 길었을 때 주욱 따라왔던 스케일링 공식을 그대로 적용하면 채널 길이가 3나노인 트랜지스터랑 성능이랑 비슷합니다 << 이런 마케팅 용어에 가까워졌음

물론 선폭 자체는 계속 줄여왔기 때문에 채널 길이가 십수~수십 나노미터 수준은 됨

아 참고로 이건 로직 공정에 대한 이야기고

메모리 공정의 경우 내가 알기로 메모리 셀 간 거리를 보고 몇 나노 공정이라고 하는 걸로 알고 있음

그래서 메모리 공정이 말로는 10몇나노 공정이니 하는데 로직 공정에 대응하면 20몇나노 수준 성능 나온다나 뭐라나

이거 진지하게 몇명이나 볼려나

c'ex